Journal of Chemical and Pharmaceutical Sciences

# **Optimization of IP filters using TCAM Architecture**

S. Rajesh, M. Sundararajan\*

Department of ECE, Bharath University, Chennai.

\*Corresponding author: E-Mail: msrajan69@gmail.com

#### ABSTRACT

By giving a stage information to the OP-AMP we can check the CMFB and Stability of the OP-AMP. Swing was not achievable in. A  $\pm$  25mV stage from Common Mode Voltage (VC) of 750mV is given as info in Unity Gain Configuration with R<sub>i</sub> & R<sub>f</sub> of 10K $\Omega$  and the outputs VOP& VON are plotted as appeared in Fig. 13. The normal of the two differential output is additionally plotted to guarantee that the CMFB is working appropriately for our required V<sub>REF</sub> of 750 mV.A large number rate of 129 mV/ns is seen with a postponement of 1ns as appeared in Fig. 14.We can watch overshoot because of un stability of the OP-AMP shifting with burden top as appeared in Fig. 1

**KEY WORDS:** Internet Protocol (IP), memory architecture, priority encoder, Spin Transfer Torque Random Access Memory (STT-RAM)-based TCAM, ternary content addressable memory (TCAM).

## **1. INTRODUCTION**

Most memory gadgets store and recover data by tending to particular memory areas. Subsequently, this way frequently turns into the restricting variable for frameworks that depend on quick memory accesses. The time required to discover a thing put away in memory can be diminished impressively if the thing can be distinguished for access by its content as opposed to by its location. A memory that is accessed along these lines is called content-addressable memory or CAM. CAM gives a performance advantage over other memory seek calculations, for example, twofold or tree-based quests or look-aside tag cradles, by contrasting the sought data against the whole rundown of pre-put away sections at the same time, regularly bringing about an order-of-extent decrease in the hunt time.

CAM is in a perfect world suited for a few capacities, including Ethernet address lookup, data pressure, design recognition, reserve labels, high-transfer speed address filtering, and quick lookup of steering, client benefit and security or encryption data on a packet-by-packet premise for high-performance data switches, firewalls, extensions and switches.

We utilize CAM in blocking specific site or made to go about as IP filter. An IP filter is a security highlight that limits unapproved access to LAN resources or confines activity on a WAN connection (IP movement that experiences the switch). IP filters can be utilized to limit the sorts of web movement that are allowed to access a LAN, and LAN workstations can be confined to particular web based applications, (for example, email). CAM can be utilized to act as a filter which hinders all access with the exception of those packets that are given unequivocal consents as indicated by the standards of the IP filter. In this undertaking, CAM thinks about the packet being directed to the port against the IP filter rules. As CAM can look data in single operation this blocking done in quick way furthermore offbeat pursuit is followed which mean if data MSB is not coordinated the hunt is not did, so unmatched site found without seeking LSB content. This save time and power of the system.

#### 2. METHODS & MATERIALS

**Existing Method:** Existing framework make SRAM to go about as TCAM.SRAM devour more power contrasted and STT RAM. In this framework synchronous hunt is followed. Data present in SRAM can discovered strictly when preparing all data. Seek operation is conveyed regardless of the possibility that data is not present in memory due to this power and time squandered.

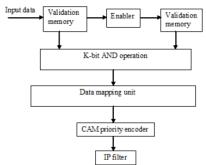

Figure.1. Architecture of TCAM

In existing framework data given of N sub words which comprises of W bits is given to cross breed apportioning and isolated into vertical rows and section for simple seeking then it is mapped in approval memory

## Journal of Chemical and Pharmaceutical Sciences

and data location is found in OATAM and OAT. In the event that data is available in two area or layer then LPE will pick address as indicated by need and create best result.

**Proposed Method:** To decrease power and time utilization in existing framework. In proposed framework STT RAM is utilized as a part of spot of SRAM for diminishing power and offbeat strategy is used. STT RAM is made to go about as CAM. In offbeat technique at first MSB of data is sought if MSB is available in memory then it begins looking LSB else it prematurely ends operation so the bungled data can found in beginning stage so power and time is devoured and contrasted and existing framework .

After above pursuit operation location of data is given to IP filter. IP filter is predominantly used to square specific packet, (for example, facebook). Packet to be blocked is enlisted and CAM thinks about the packet being directed to the port against the IP filter rules. At the point when a match is found, the packet is either allowed or denied.

**Block diagram explanation:** The Fig 2 represents the architecture layer. It has M layers and a TCAM priority encoder. Each layer output is given to potential match address. The PMAs are given to CPE, which selects match address among PMA.

Figure.2. Block diagram of IP filter using TCAM

Block diagram is shown in Fig: 2. It contains L validation memories, k-bit AND operation, O real address table address memories, P real address tables, K-bit ANDed operation, TCAM priority encoder and IP filter.

**Validation Memory:** Capacity of all VM is  $2w \times E$  bits where w speaks to the quantity of bits in every subword and 2w demonstrates the quantity of rows. A subword of w bits suggests that it had complete blends of 2w where every mix speaks to a subword. For instance, if w is of 8 bits, then it meant that there are aggregate of 32 = 24 combinations. This clarification is additionally identified with OATAM and OAT. Everysubword goes about as a location to VM. On the off chance that the memory area are summoned by a subword is too large, it implies that the information subword is available, generally missing. In this way, VM accepts the information subword, in the event that it is available. MSB of data is at first checked and if data is available it empowers next VM. if MSB data is not present operation is prematurely ended. On the off chance that MSB is available then LSB hunt is completed.

For instance, Table demonstrates that subwords 00, 0x, and xx are mapped in VM21. This states memory areas 00, 0x, and xx ought to be peak in VM21 and the remaining memory areas are set to 0V in light of the fact that their comparing subwords don't exist

**K-bit ANDed Operation:** The output of 1-bit AND operation chooses the serial operation. On the off chance that the consequence of 1-bit AND operation is 5V, then it allows the serial operation, generally jumble happens in the relating layer.

**Data mapping unit:** Each OATAM (Original Address Table Address Memory) is of  $2E \times E$  bits where 2E is the quantity of rows and every row has E bits. In OATAM, a location was put away on the memory area filed by a subword and that deliver is then used to conjure a row from its comparing OAT (Original Address Table). On the off chance that a subword in VM is located, then a relating location is likewise put away in OATAM at a memory area accessed by the subword. For instance, Table 3.2 illustrates OATAM21 where locations are put away at the memory areas 00, 0x, and xx. The output of OATAM is called as OATA.

Measurements of OAT are  $2E \times K$  where E is the quantity of bits in a subword, 2E speaks to number of rows, and K is the quantity of bits in every row where every piece speaks to a unique location. Here K is a subset of unique locations from traditional TCAM table. It is OAT, which considers the capacity of unique locations.

**CAM priority encoder:** More than one match may occur in TCAM, the LPE selects PMA from the outputs of data mapping unit.

**IP filter:** IP filter is used for security purpose. Used to block unauthorized access to LAN resource or restricts traffic on a WAN link (IP traffic that goes through the router). The packet should be allowed is stored and when TCAM gives address from data fed and this is compared with stored table if address matches the packet is allowed. If packet is not in table packet is blocked.

# Operations

## Journal of Chemical and Pharmaceutical Sciences

**Data Mapping Operation:** Established TCAM lookup table is coherently parceled into mixture partitions. Every half and half segment is then ventured into a parallel variant. In this way, we first extend x into states 0 and1 to be put away in STT RAM. For instance, in the event that we had a TCAM expression of 0110xs, then it is ventured into 01100 and 01101. Each subword, going about as a location, is connected to its comparing VM (Validation Memory), rationale "1" is composed at that memory area. The same subword is likewise connected to its individual OATAM and w bits data are composed at that memory area. The K bits data are likewise composed at the memory area in OAT dictated to its relating OATA. Along these lines, thusly, all half and half parcels are mapped.

| Tabl | e.1. | loo | kup | table |

|------|------|-----|-----|-------|

|------|------|-----|-----|-------|

| ADDR | SW1 | SW2 | Layer |

|------|-----|-----|-------|

| 0    | 00  | 11  | 1     |

| 1    | 01  | 01  | 1     |

| 2    | 0x  | 11  | 2     |

| 3    | 11  | 1x  | 2     |

#### Table.2. Data mapping in validation memory and OATAM

| AD | V  | V  | V  | V  | OA | OA | OA | 0  |

|----|----|----|----|----|----|----|----|----|

| DR | Μ  | Μ  | Μ  | Μ  | TA | TA | TA | Α  |

|    | 11 | 12 | 21 | 22 | Μ  | Μ  | М  | Т  |

|    |    |    |    |    | 11 | 12 | 21 | Α  |

|    |    |    |    |    |    |    |    | Μ  |

|    |    |    |    |    |    |    |    | 22 |

| 0  | 1  | 0  | 1  | 0  | 0  | -  | 0  | -  |

| 1  | 1  | 1  | 1  | 0  | 1  | 0  | 1  | -  |

| 2  | 0  | 0  | 0  | 1  | -  | -  | -  | 0  |

| 3  | 0  | 1  | 1  | 1  | -  | 1  | 2  | 1  |

#### Table.3. Data mapping in OAT

| ADDR | OAT11 | OAT12 | OAT21 | OAT22 |  |  |  |

|------|-------|-------|-------|-------|--|--|--|

|      | 01    | 01    | 23    | 23    |  |  |  |

|      |       |       |       |       |  |  |  |

| 0    | 10    | 01    | 10    | 01    |  |  |  |

| 1    | 01    | 10    | 10    | 11    |  |  |  |

| 2    | 00    | 00    | 01    | 00    |  |  |  |

| 3    | 00    | 00    | 00    | 00    |  |  |  |

#### Table.4. Address of data fed

|      |    |    |        |                 | Orig | inal | Addre | ess |

|------|----|----|--------|-----------------|------|------|-------|-----|

| Addr | v  | v  | OAT    | OATA            | OAT  | 2    | OAT   | 22  |

| ess  | Μ  | Μ  | $AM_2$ | M <sub>22</sub> | 1    |      | 2     | 3   |

|      | 21 | 22 | 1      |                 | 2 3  |      |       |     |

| 0    | 1  | 0  | 0      | -               | 1    | 0    | 0     | 1   |

| 1    | 1  | 0  | 1      | -               | 1    | 0    | 1     | 1   |

| 2    | 0  | 1  | -      | 0               | 0    | 1    | 0     | 0   |

| 3    | 1  | 1  | 2      | 1               | 0    | 0    | 0     | 0   |

A sub word in a cross breed parcel able to be available in various locations. Thus, it is pointed in its relating VM and its unique location is pointed to its comparing bits in its individual OAT. Since a solitary piece in OAT speaks to a unique location, just those memory areas in VMs and address positions unique locations in OATs are high, which are noted while rest of the memory areas and address positions are set to low in VMs and OATs, separately. Case of data mapping is appeared in Table 3.2. We utilize Table I to be mapped. We take N = 2, M = 2, K = 2, and E = 2. After essential preparing, Cross breed segments of layer 1 can be effortlessly mapped in comparative way.

**Search Operation:** W subwords are concurrently connected to a layer. Subwords at first connected to the empower here first MSB bits are looked if data is discovered then it begin seeking LSB bits so power and time utilization is diminished. The subwords then read out their comparing memory areas from their separate VMs. In the event that all VMs accept their comparing subwords, then looking will proceed, generally crisscross happens in the layer.

## Journal of Chemical and Pharmaceutical Sciences

Endless supply of all subwords, the subwords read out their separate memory areas from their relating OATAMs concurrently and output their comparing OATAS.

TCAM gives location of data present in STT RAM with the goal that data can be acquired from STT RAM in single cycle so power utilization and time is all that much diminished here nonconcurrent data seeking is followed this additionally lessen devouring power from framework

**IP filter Operation:** An IP filter is a security highlight that forbids unapproved clients from accessing LAN resources. It can likewise limit IP movement over a wide-area network (WAN) join. With an IP filter, LAN clients can be limited to particular applications on the Internet, (for example, facebook). CAM fills in as a filter to hinder all access aside from packets that have consent. The locations that have consent are put away in CAM; when a location is sent to memory, CAM reports whether it contains the location. On the off chance that the location dwells inside of CAM, it has consent for a specific action.

| Address | Data       | Filter<br>rule | Routed | Permission |

|---------|------------|----------------|--------|------------|

| 0       | 01         |                | Packet |            |

| 1       | 27         | <b>←</b> →     | 27     | Permit     |

| 2       | 3 <b>A</b> |                | 3A     | Permit     |

| 3       | 4D         |                | 4F     | Denied     |

|         |            |                | 25     | Denied     |

# Figure.3. IP Filter lookup table

#### **3. RESULTS AND DISCUSSION** Existing system parameter analysis Summary of timing:

Speed Grade: 7

Minimum period: 4.148ns (Maximum Frequency: 241.080MHz)

Minimum input arrival time before clock: 2.870ns

Maximum output required time after clock: 6.229ns

Maximum combinational path delay: No path found

#### **Design Summary**

Number of errors: 0 Number of warnings: 3 Logic Utilization: Total Number Slice Registers: 13 out of 13,824 1% Number used as Flip Flops: 10 Number used as Latches: 3 Number of 4 input LUTs: 10 out of 13,824 1% Logic Distribution: Number of occupied Slices: 10 out of 6,912 1% Number of Slices containing only related logic: 10 out of 10 100% Number of Slices containing unrelated logic: 0 out of 10 0% Total Number of 4 input LUTs10 out of 13,824 1% Number of bonded IOBs: 6 out of 510 1% IOB Flip Flops: 1 IOB Latches: 1 Number of GCLKs: 1 out of 4 25% Peak Memory Usage: 134 MB

Figure.4. Existing system Xilinx Simulation output

July - September 2016

S -201

| Power summary:                     | I(mA) | P(mW) |

|------------------------------------|-------|-------|

| Total estimated power consumption: |       | 54    |

| Vcc int 1.80V:                     | 26    | 47    |

| Vcco33 3.30V :                     | 2     | 7     |

| Clocks:                            | 0     | 0     |

| Inputs:                            | 7     | 13    |

| Logic:                             | 4     | 7     |

| Vcco33                             | 0     | 0     |

| Signals:                           | 0     | 0     |

| Quiescent Vcc int 1.80V:           | 15    | 27    |

| Quiescent Vcco33 3.30V:            | 2     | 7     |

This is result and analysis of existing system which use SRAM and synchronous method for searching data in memory and this is overcome in proposed system.

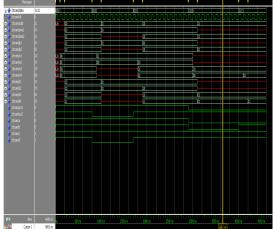

Proposed system result and analysis: **Timing Summary:** Speed Grade: -7 Minimum period: 2.722ns (Maximum Frequency: 367.377MHz) Minimum input arrival time before clock: 3.203ns Maximum output required time after clock: 6.229ns Maximum combinational path delay: 7.809ns Design Summary Number of errors: 0 Number of warnings: 1 Logic Utilization: Number of Slice Flip Flops: 9 out of 13,824 1% Number of 4 input LUTs: 8 out of 13,824 1% Logic Distribution: Number of occupied Slices: 11 out of 6,912 1% Number of Slices containing only related logic: 11 out of 11 100% Number of Slices containing unrelated logic: 0 out of 11 0% Total Number of 4 input LUTs: 8 out of 13,824 1% Number of bonded IOBs: 8 out of 510 1% IOB Flip Flops: 1 IOB Latches: 1 Number of GCLKs: 1 out of 4 25% Number of GCLKIOBs: 1 out of 4 25% Total equivalent gate count for design: 133 Additional JTAG gate count for IOBs: 432 Peak Memory Usage: 134 MB

Figure.5. Output waveform of proposed system

## 4. CONCLUSION

The utilization of nonconcurrent and STTRAM in IP filter will build pace of inquiry data so that bottleneck in packet sending is abundantly diminished and expand high throughput sending in switches. The examination result utilizing this building design is confirmed and this demonstrates the power and time is extremely lessened contrasting and existing framework.

## www.jchps.com REFERENCES

Anh-Tuan Do, Shoushun Chen, Zhi-Hui Kong, and KiatSeng Yeo, A High Speed Low Power CAM With a Parity Bit and Power-Gated ML Sensing, IEEE Transactions On Very Large Scale Integration Systems, 21(1).

Chengen Yang, YunusEmre, Yu Cao and Chaitali Chakrabarti, Improving Reliability Of Non-Volatile Memory Tech Nologies Through Circuit Level Techniques And Error Control Coding, Yang et al. EURASIP Journal on Advances in Signal Processing, 2012.

DejanGeorgiev PhD Student, Faculty of Electrical and Information Technologies- Skopje, Macedonia, Low Power Concept For Content Addressable Memory Chip Design, Copyright to IJAREEIE, 2(7), 2013.

Gopalakrishnan K, Sundar Raj M, Saravanan T, Multilevel inverter topologies for high-power applications, Middle - East Journal of Scientific Research, 20(12), 2014, 1950-1956.

Jasmin M, Vigneshwaran T, Beulah Hemalatha S, Design of power aware on chip embedded memory based FSM encoding in FPGA, International Journal of Applied Engineering Research, 10(2), 2015, 4487-4496.

Jiang W and Prasanna V, Parallel IP lookup using multiple SRAM based pipelines, in Proc. IEEE Int Symp Parallel Distrib.Process, 2008, 1–14.

Jiang w and Prasanna V, S calable packet classification on FPGA, IEEE Trans. Very Large Scale Integr Syst, 20(9), 2012, 1668–1680.

Kanniga E, Selvaramarathnam K, Sundararajan M, Kandigital bike operating system, Middle - East Journal of Scientific Research, 20(6), 2014, 685-688.

Kanniga E, Sundararajan M, Modelling and characterization of DCO using pass transistors, Lecture Notes in Electrical Engineering, 86(1), 2011, 451-457.

Karthik B, Arulselvi, Noise removal using mixtures of projected gaussian scale mixtures, Middle - East Journal of Scientific Research, 20(12), 2014, 2335-2340.

Karthik B, Arulselvi, Selvaraj A, Test data compression architecture for lowpower vlsi testing, Middle - East Journal of Scientific Research, 20(12), 2014, 2331-2334.

Karthik B, Kiran Kumar T.V.U, Authentication verification and remote digital signing based on embedded arm (LPC2378) platform, Middle - East Journal of Scientific Research, 20(12), 2014, 2341-2345.

Karthik B, Kiran Kumar T.V.U, EMI developed test methodologies for short duration noises, Indian Journal of Science and Technology, 6(5), 2013, 4615-4619.

Karthik B, Kiran Kumar T.V.U, Vijayaragavan P, Bharath Kumaran E, Design of a digital PLL using 0.35Î<sup>1</sup>/4m CMOS technology, Middle - East Journal of Scientific Research, 18(12), 2013, 1803-1806.

Nitin Mohan, Student Member, IEEE, Wilson Fung, Member, IEEE, Derek Wright, Student Member, IEEE and ManojSachdev, Senior Member, IEEE, Design Techniques And Test Methodology For Low-Power Tcams, Ieee Transactions On Very Large Scale Integration (Vlsi) Systems, 14(6), 2006.

Pagiamtzis K and Sheikholeslami A, Content-addressable memory circuits and architectures, A tutorial and survey, IEEE J Solid- State Circuits, 41(3), 712–727, 2006.

Philomina S, Karthik B, Wi-Fi energy meter implementation using embedded linux in ARM 9, Middle - East Journal of Scientific Research, 20(12), 2014, 2434-2438.

Ping Zhou, Bo Zhao, Jun Yang, Youtao Zhang Electrical and Computer Engineering Department, Department of Computer Science University of Pittsburgh, Energy Reduction For Stt-Ram Using Early Write Termination, International Symposium on Quality Electronic Design, 2011.

SarangDharmapurikar, Dept of Comput Sci & Eng, Washington Univ, St Louis, MO, USA, Praveen Krishnamurthy, Taylor D.E, Longest Prefix Matching Using Bloom Filters, Networking, IEEE/ACM Transactions on, 14(2), 2007.

Saravanan T, Sundar Raj M, Gopalakrishnan K, Comparative performance evaluation of some fuzzy and classical edge operators, Middle - East Journal of Scientific Research, 20(12), 2014, 2633-2633.

Saravanan T, Sundar Raj M, Gopalakrishnan K, SMES technology, SMES and facts system, applications, advantages and technical limitations, Middle - East Journal of Scientific Research, 20(11), 2014, 1353-1358.

## Journal of Chemical and Pharmaceutical Sciences

Satendra Kumar Maurya and Lawrence T, Clark, Senior Member, IEEE, A Dynamic Longest Prefix Matching Content Addressable Memory for IP Routing, IEEE Transactions On Very Large Scale Integration Systems, 19(6), 2011.

Shanq-Jang Ruan, Nat Taiwan Univ of Sci & Technol, Taipei, Chi- Yu Wu, Jui-Yuan Hsieh, Low Power Design Of Precomputation-Based Content-Addressable Memory, Very Large Scale Integration Systems, IEEE Transactions on, 16(3), 2008.

Vijayaragavan S.P, Karthik B, Kiran Kumar T.V.U, A DFIG based wind generation system with unbalanced stator and grid condition, Middle - East Journal of Scientific Research, 20(8), 2014, 913-917.

Vijayaragavan S.P, Karthik B, Kiran Kumar T.V.U, Effective routing technique based on decision logic for open faults in fpgas interconnects, Middle - East Journal of Scientific Research, 20(7), 2014, 808-811.

Vijayaragavan S.P, Karthik B, Kiran Kumar T.V.U, Privacy conscious screening framework for frequently moving objects, Middle - East Journal of Scientific Research, 20(8), 2014, 1000-1005.

ZahidUllah, Manish K, Jaiswal and Ray C. C, Cheung, Z-TCAM, An SRAM-based Architecture for TCAM, IEEE transactions on very large scale integration systems, 2014.